# **SynFox** HIGH RESOLUTION Frac-N SYNTHESIZER

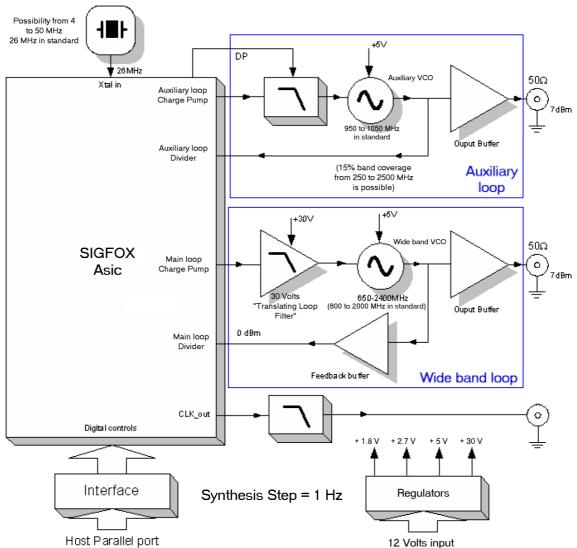

*SynFox* is a high performance dual synthesizer module based on *High Resolution Multi-Accumulator Fractional-N synthesis* technology and comprising a narrow band 950MHz-1050MHz and a wide band 800MHz-2GHz fast and ultra low noise loop (standard configuration). Frequency plan can be extended from 0 to 3 GHz on customer request.

It exhibits outstanding performance of high resolution (1Hz steps), low phase noise (Better than -100dBc/Hz @ 1kHz) and very short lock times (40us for 1MHz step). It includes all the necessary circuitry to support FM/GMSK Dual port modulation from the narrowband PLL as well as generate 4 output clocks from the main crystal (/1, /2, /4, /8).

This module is ideally fitted for various radio product designs, ranging from low cost *RF generator*, to *spectrum analyzer*, *high accuracy sources*, or *Software Definable Radio (SDR) transceivers*. It provides a very attractive replacement for **DDS** based systems at much reduced cost for equivalent or better performance.

# SynFox Highlights

- Dual Frac-N synthesizers 0-3GHz

- Outstanding 1Hz resolution thanks to Sigma Delta Frac-N technology

- best in class resolution (1Hz), phase noise & lock time

- Programming support available for various µC, Windows, or Linux

- High performance & Low Cost alternative to DDS-based synthesizers & generators

# <u>APPLICATIONS</u> : RF GENERATORS, SPECTRUM ANALYZERS, SOFTWARE DEFINABLE RADIOS, HIGH ACCURACY RF and MICROWAVE SOURCES

Metal housing version

# **Order Entry :**

| Part number             | packaging     | description                     |

|-------------------------|---------------|---------------------------------|

| <b>SynFox-</b> 0.8/2-1G | РСВ           | One wide band loop 0.8 to 2GHz  |

|                         | Metal Housing | One Narrow loop 950 to          |

|                         |               | 1050MHz)                        |

| <b>SynFox-</b> 0.8/2-G  | Metal Housing | One single 0.8 to 2GHz Loop     |

| <b>SynFox-</b> x/x-xG   | Metal Housing | Frequency plan on demand from   |

| Upon customer request   | _             | 0 to 3GHZ either in single loop |

|                         |               | or dual loop configuration      |

SigFox

#### **SPECIFICATIONS** Wide band Synthesizer

| Parameter                 | Unit    | Value                         | Comment                                                                            |

|---------------------------|---------|-------------------------------|------------------------------------------------------------------------------------|

| Minimum frequency         | MHz     | 800                           |                                                                                    |

| Maximum frequency         | MHz     | 2000                          |                                                                                    |

| Minimum frequency<br>step | Hz      | 1.16                          | 1 Hz software interpolation<br>All other kind of steps configurable<br>by Software |

| Reference frequency       | MHz     | 26                            |                                                                                    |

| Output power              | dBm     | 10                            |                                                                                    |

| Phase Noise               | dB/ Hz  | Typ : -105 dBc / Hz           | Within the loop bandwidth                                                          |

| Discrete Spurious         | dBc     | -80                           | $\Delta F > 600 \text{ KHz}$                                                       |

| Kvco                      | MHz / V | 40 to 60                      |                                                                                    |

| Loop filter bandwidth     | KHz     | 200                           |                                                                                    |

| Settling time             | μs      | 500 typ                       | 10 MHz step                                                                        |

| Tests mode                | -       | Force Up, Down<br>Accumulator | Min or Max frequency.<br>0, 1, 2 or 3 accumulators.                                |

|                           |         | number<br>Current reduction   | Current / Max. freq. Reduction.<br>Possibility to tune 'decade'                    |

|                           |         | Decade tuning                 | frequency.                                                                         |

# Auxiliary Synthesizer with FM / GMSK / Dual Port modulation

| Parameter             | Unit   | Value               | Comment                                             |

|-----------------------|--------|---------------------|-----------------------------------------------------|

| Minimum frequency     | MHz    | 950                 |                                                     |

| Maximum frequency     | MHz    | 1050                |                                                     |

| Minimum frequency     | Hz     | 1.55                | 1 Hz software interpolation                         |

| step                  |        |                     | All other kind of steps configurable<br>by Software |

| Reference frequency   | MHz    | 26                  |                                                     |

| Output power          | dBm    | 8                   |                                                     |

| Phase Noise           | dB/ Hz | Typ : -105 dBc / Hz | Within the loop bandwidth                           |

| Discrete Spurious     | dBc    | -79                 | $\Delta F > 600 \text{ KHz}$                        |

| Loop filter bandwidth | KHz    | 150                 |                                                     |

| Settling time         | μs     | 100 max             | 100 MHz step                                        |

| Total phase Error     | deg    | 1.2 max             | Can also easily be modulated                        |

| with internal GMSK    |        |                     | through the crystal within a 0 to 100               |

|                       |        |                     | KHz BW                                              |

| Modulation mask @     | dBc    | -70 dBc             | With the Dual Port                                  |

| 400 KHz for typical   |        | N/A                 | Without the Dual Port                               |

| GSM modulation        |        | N/A                 | Dual Port alone                                     |

| (GMSK)                |        |                     |                                                     |

| PLL Tests mode        | -      | Modulation          | Random, '0101', or High-Z                           |

|                       |        | Accumulator         | 0, 1, 2 or 3 accumulators.                          |

|                       |        | number              | From 0 to $600\mu A$                                |

|                       |        | Charge-pump         | Current / Max. Freq. Reduction.                     |

|                       |        | Current Current     | Phase noise reduction @ 400 KHz                     |

|                       |        | reduction           |                                                     |

|                       |        | Notch               |                                                     |

| Dual Port test        | -      | DP-Gain, DP-Delay   | For Dual Port optimization                          |

|                       |        | and DP-Gain-ana     |                                                     |

# **Output CLOCKs**

| Parameter               | Unit | Value                                         | Comment                                      |

|-------------------------|------|-----------------------------------------------|----------------------------------------------|

| Clocks number           | -    | 1 from 4 on the IC                            |                                              |

| Mode                    | -    | ON, OFF (high-Z)<br>Analog or Digital<br>CMOS |                                              |

| Division ratio          | -    | 1, 2, 4 or 8                                  |                                              |

| Clock output voltage    | Vpp  | l<br>Logic_VCC                                | Analog mode (sinewave)<br>CMOS mode (square) |

| Clock output mean value | V    | Logic_VCC / 2                                 | 0.9 V if Logic_VCC = 1.8V                    |

| Filtering               | -    | -                                             | Internal lowpass                             |

# **Physical parameters**

| Parameter           | Unit | Value              | Comment                                                       |

|---------------------|------|--------------------|---------------------------------------------------------------|

| PCB dimensions      | mm   | 105 x 59           | Max dimensions                                                |

| Interface connector | -    | SubD 25 compatible | Male connector must be mounted for PC Centronic compatibility |

| RF outputs          | -    | Connector or cable | Compatible with PCB mounted SMA, BNC or 50 Ohms cables        |

Host Parallel port